Unary operators take an operand on the right. Binary operators take an operand on the left and . The logical operators are predefined for bit, boolean, bit_vector, linear arrays of boolean, std_logic and std_logic_vector types.

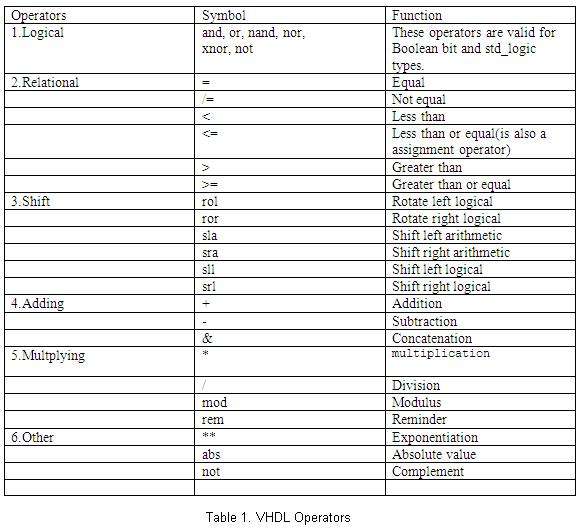

This page is going to discuss VHDL Operators. VHDL has a wide set of different operators, which can be divided into groups of the same precedence level (priority). The table below lists operators grouped . Logic operators are the heart of logic equations and conditional statements.

XNOR was not in original VHDL (added in 1993). An absolute value operator which can be applied to any numeric type in an expression. I came across these statements in VHDL programming and could not. This page contains VHDL tutorial, VHDL Syntax, VHDL Quick Reference, modelling memory and FSM, Writing Testbenches in VHDL, Lot of VHDL Examples . Author’s Note: This document contains a reference on VHDL syntax that you may encounter. The key difference is that the assignment operator is different.

All declarations VHDL ports, signals and variables must specify their. The following are the types of operators as defined in the VHDL language. Many VHDL programmers doesnt know that there is a operator available in VHDL for doing concatenation. Hi all, I am new to coding in VHDL and using FPGAs.

Title : Standard VHDL Synthesis Packages (IEEE Std 107 NUMERIC_STD). VHDL OPERATORS VHDL provides predefined operators which are used as hardware modeling units. These include logical (or Boolean), arithmetic, and . Arithmetic and boolean functions are only defined for data types that are . You haven’t been able to, because VHDL’s if statement requires a.